# **Comparative Study of Diode Clamped Multilevel Inverter**

M. Hafiz Arshad, Baharuddin Ismail, Azralmukmin Azmi, M. Z. Mohd Radzi School of Electrical Engineering, Univ. of Malaysia Perlis.

adik\_arshad@yahoo.com

## **Abstract**

This paper presents simulation focus in a single phase diode clamped multilevel inverter topology also known as Neutral Point Clamped. Circuit will construct and simulate by using PSIM software and the solution is based on series connection of three to ninelevel diode clamped inverters modules. IGBT devices are used almost exclusively in this power range. The more level can be produce, it does will be much better for the application. It is because the value of THD also will decrease once the levels of the multilevel inverter increase. The simulation result shows the total harmonic distortion (THD) for three, five, seven and nine level of diode clamped topologies.

### 1. Introduction

Concept of the multilevel inverter is san as the other inverter which is to converts exect current (De) to alternating current (AC); the converted AC can be at any required voltage and frequency of the use of appropriate transformers a switching, and control circuits [1]. From the source that the inverter will convert the DC electricity to AC electricity [2]. In this modern technology, Power electronistiss is very important where it used in a great variety of product. With the high potential is high power for industry, multilevel inverter will become most appular for so many applications.

The devlopm ats to use this topology because it's have so many advantages. There have three main features by using multilevel inverter. The most reason is ability to reduce the voltage stress on each power device due to the utilization of multiple levels on the DC bus. Even at low switching frequencies, smaller distortion in the multilevel inverter AC side waveform can be achieved with the step modulation technique. Such as in traction system, when a high DC side

voltage is imposed by an application is very important [3].

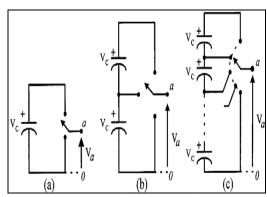

Multilevel inverters in ` semiconductors and apacitr on sources. Output voltages of multipled vertes include the additions of the capacitor of tages de to the commutation of the switches. Figure shows schematic diagram of one phase leg f inverers with several numbers of levels. The action power remiconductors is represented by switch with several actions. A two level vert ; as s n in Figure 1 (a), generates an output voltage of two levels with respect to the negative terninal the capacitor, while the three-level inverter shown in Figure 1 (b) generates three voltages, and so n. hus, the output voltages of multilevel inverters e several levels. Moreover, they can reach high voltage, while the power semiconductors must withstand only reduced voltages [4].

Figure 1: One phase leg of an inverter (a) Two levels, (b) Three levels, and (c) *n* levels

### 2. Diode Clamped Topology

The diode clamped inverter more focus on low frequency applications. Also known as Neutral Point Clamped inverter was introduced in early 80's and has been extensively used today in various applications. In early 90's, there have several authors were extended

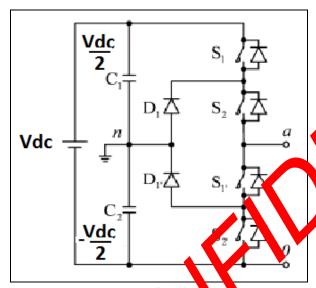

the concept from three level to multilevel inverter. But there have no reports in practical applications been recorded yet. As shown in Figure 2 is the circuit diagrams for three and five level of diode clamped structure.

Based on concept of using diodes is to limit power devices voltage stress. The output voltage distortion is very low due to multiple levels in the output voltages. The *dv/dt* of switches is low since the switches used to reduced voltage. The switches can operate at a lower switching frequency. In the applications of motor drives, the input currents have low distortions and the common-mode voltages are reduced. The common-mode voltages can be eliminated using sophisticated modulation methods [5].

Figure 2: Three Level of Figure 2: Three Level

Figure 2 show the diele camped of multilevel inverter circuit topologies. The structure and basic principle is consists of series connected capacitors that divide DC bus voltage and a set of capacitor voltages. In Figure 2, it's shown for the three levels diode clamped everter DC bus is split by two seriesconnected be in capacitors, C1 and C2. The n can be defined as the neutral point (between two capacitors).

There will be three states for the output voltage which is Vdc/2, 0 and -Vdc/2. These two diode, (D1 and D1') was clamped the switch voltage to half the level of the dc-bus voltage. The sequences when S1 and S2 is turn ON, the voltage across a and 0 is equal

with Vdc. In this states, the function of D1' is to balances out the voltage sharing between S1' and S2'. While S1' and S2' blocking the voltage across C1 and C2 to become Vdc/2.

# 3. Methodology

All procedures are using the same parameter as in Table 1.

Table 1: Input Parameter

| Input and Load Parameter                      |                  |  |  |  |  |  |  |

|-----------------------------------------------|------------------|--|--|--|--|--|--|

| Input Voltage                                 | 36CV             |  |  |  |  |  |  |

| Fundamental Frequency                         | 50Hz             |  |  |  |  |  |  |

| Resistary (Load)                              | 100 ohm          |  |  |  |  |  |  |

| Sinusoid Voltag Source Parameter (Modulation) |                  |  |  |  |  |  |  |

| ok A uplitude                                 | 1000V            |  |  |  |  |  |  |

| Moc lation Frequency                          | 50Hz             |  |  |  |  |  |  |

| Triangular-wave Voltage (Carrier)             | Source Parameter |  |  |  |  |  |  |

| V Peak to Peak                                | 100V             |  |  |  |  |  |  |

| Carrier Frequency                             | 5KHz             |  |  |  |  |  |  |

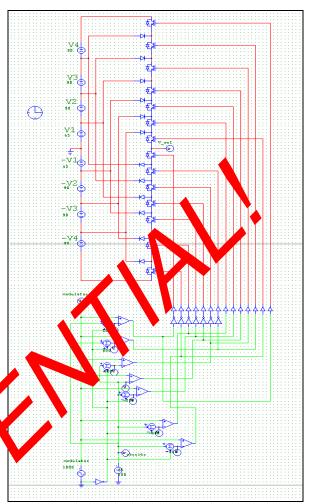

Table 2 show the operation and the characteristic of the switch states for the three-level diode clamped multilevel inverter. Figure 3 shows the schematic circuit for the three level diode clamped multilevel inverter.

Table 2: Three-level diode clamped multilevel inverter voltage levels and corresponding switch state.

| Voltage | Switch State |    |     |     |  |  |

|---------|--------------|----|-----|-----|--|--|

|         | S1           | S2 | S1' | S2' |  |  |

| VDC/2   | 1            | 1  | 0   | 0   |  |  |

| 0       | 0            | 1  | 1   | 0   |  |  |

| -VDC/2  | 0            | 0  | 1   | 1   |  |  |

Figure 3: A single-phase three-level diode clamped multilevel inverter circuit.

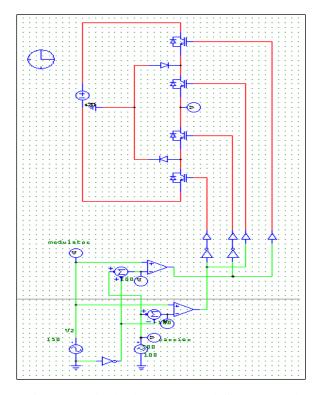

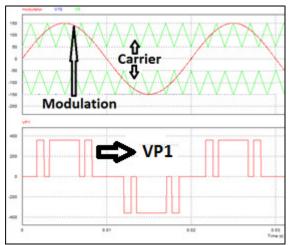

For control the signal, pulse width mode ation (PWM) is the best and easiest technique in controlling the active devices in a multilevel inverter. The WM method uses several triangle carrier signal and modulation to generate switching signals by comparing between them [6]. Figure 4 shows the basic principle to show the comparison applied to find the output voltage.

Figure 4: PWM modulation of nine-level DCMLI

Figure 5: A single-phase nine-level diode clamped multilevel inverter circuit

Referred to the figure 5, it can be seen that each switching device is required to block only a voltage level of Vdc, the clamping diodes required different rating for reverse voltage blocking. For example the last switching state where is when all the switch from S1' to S7' is turn ON, the following diode must block - V1. Same like for the other state. That show about the number of blocking diodes is quadratically relates to the number of levels in a diode clamped topology.

Table 3: Nine-level diode clamped multilevel inverter voltage levels and switch state.

| Voltage |    | Switch State |    |    |    |    |    |     |     |     |     |     |     |     |

|---------|----|--------------|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| (V)     | S1 | S2           | S3 | S4 | S5 | S6 | S7 | S1' | S2' | S3' | S4' | S5' | S6' | S7' |

| V1      | 1  | 1            | 1  | 1  | 1  | 1  | 1  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| V2      | 0  | 1            | 1  | 1  | 1  | 1  | 1  | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| V3      | 0  | 0            | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 0   | 0   | 0   | 0   | 0   |

| V4      | 0  | 0            | 0  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 0   | 0   | 0   | 0   |

| -V4     | 0  | 0            | 0  | 0  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| -V3     | 0  | 0            | 0  | 0  | 0  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 0   | 0   |

| -V2     | 0  | 0            | 0  | 0  | 0  | 0  | 1  | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

| -V1     | 0  | 0            | 0  | 0  | 0  | 0  | 0  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

Table 3 shows the nine-level diode clamped multilevel inverter voltage levels and switching state for the circuit diagram in Figure 5. The sequences could be elaborate such as:

For voltage level Van = V1, turn on all upper switches  $S1 \sim S7$ .

For voltage level Van = V2, turn on upper switches S2 ~ S7 and lower switch S1'.

For voltage level Van = V3, turn on upper switches S3 ~ S7 and lower switches S1' and S2'.

For voltage level Van = V4, turn or apper twitches S4 ~ S7 and lower switches S1' ~ S34.

For voltage level Van = -Verturn of upper switches S5 ~ S7 and lower switches S1 S4

For voltage level V(n = -V), the on upper switches S6 ~ S7 and lower sweches S1' S5.

For voltage level Va. 2, turn on upper switch S7 and lower switches \$1'~ S6'.

For voltage well an = -V1, turn on all lower switches  $S1' \sim S7'$ .

### 4. Result and Discussion

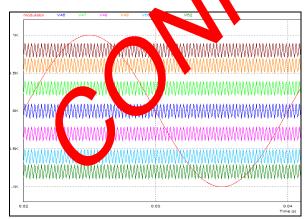

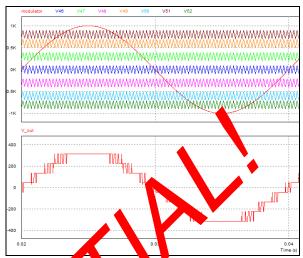

Figure 6 shows the output voltage of the single phase nine-level diode clamped multilevel inverter by using PWM method. To control the circuit, Pulse-width modulation (PWM) is a commonly technique to use for

controlling power in electrical devices and it made practical by modern electronic power switches [7].

Figure 6: Output voltage for single phase nine-level diode clamped

aster han we would affect the load, which is to say the device that uses the power. Figure 7. This is a simple in thod to generate the PWM pulse train corresponding to a given signal is the interceptive PWM: the signal (modulation) is compared with a saw tooth waveform (carrier). When the latter is less than the former, the PWM signal (VP1) is in high state (1). Otherwise it is in the low state (0).

Figure 7: Output voltage for single phase three-level diode clamped

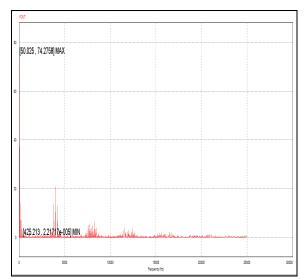

In Figure 8 and 9 below show the Total Harmonic Distortion (THD) spectrum for the output voltage in each level. Based on the simulation result its shows

there have very low THD level when increased the level of multilevel inverter [8].

Figure 8: THD spectrum for the output voltage for three level circuits

Figure 9: THD spectrum for the output voltage for nine evel orcuits.

This proved as more levels can be formed, there was less T. D hap ened. It's shown as in Table 4.

Table 4: Comparison level by THD and Current (Load)

| Stage of   | THD (%) | Current (A) |

|------------|---------|-------------|

| Multilevel |         | (LOAD)      |

| 3 Level    | 118.00  | 30.00       |

| 5 Level    | 31.27   | 15.42       |

| 7 Level    | 19.70   | 3.60        |

| 9 Level    | 11.30   | 3.15        |

When increased levels of the inverter then indirectly help to reduce the THD and can improve the performance of the application. FFT or Fast Furrier Transform was applied to the output voltage to get the THD result.

#### 5. Conclusion

As a conclusion, this paper focused about the single-phase diode-camped multilevel diverter. It was achieved the expected result by simulated the diode clamped topology with different level to compared the THD result. The circuit was designed with the PSIM software package where is easiest to use PWM method to get the result. This topology not only o reduce the harmonics distortions but can be used on the low frequency application such a far motor drives [9].

### 6. References

- [1] M. H. Ravid, "Power Electronics Circuits, Devices and Apple and "a cond edition: Prentice Hall Inc., 1988.

- [2] N. M. han, T. M. Undeland, and W. P. Robbins, "Power F' ctronic, Converters, Applications and Design", *second dition*, New York: Wiley, 1995.

- A Survey of Topologies, Controls, and Applications", *IEEE Transactions on Industrial Electronics*, Vol.49, No.4, pp. 724-738, 2002.

- [4] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point clamped PWM inverter," *IEEE Trans. Ind. Applicat.*, vol. IA-17, pp. 518-523, 1981.

- [5] S. Khomfoi and L. M. Tolbert, "Power Electronics Handbook, Multilevel Power Converters Chapter 17", *2nd Edition Elsevier*, 2007, ISBN 978-0-12-088479-7, pp. 451-482, 2007.

- [6] Baharuddin Ismail, "Design and Development of a SPWM Single Phase Inverter" Proceedings of *MUCEET*, 2009.

- [7] Baharuddin Ismail, "Microcontroller-Based SPWM Single Phase Full Bridge Inverter" *Proceedings of EnCon*, 2008.

- [8] Wang, J, Wei, R., Ge, Q., Li, Y., "The Harmonic Selection Elimination of Multilevel Converters" *IEEE International Conference on Electrical Machines and Systems*, Vol.1, pp. 419-422, 2003.